# TIA連携を活用した機能性原子薄膜テクノロジーの研究開発

SATテクノロジー・ショーケース2015

## ■はじめに

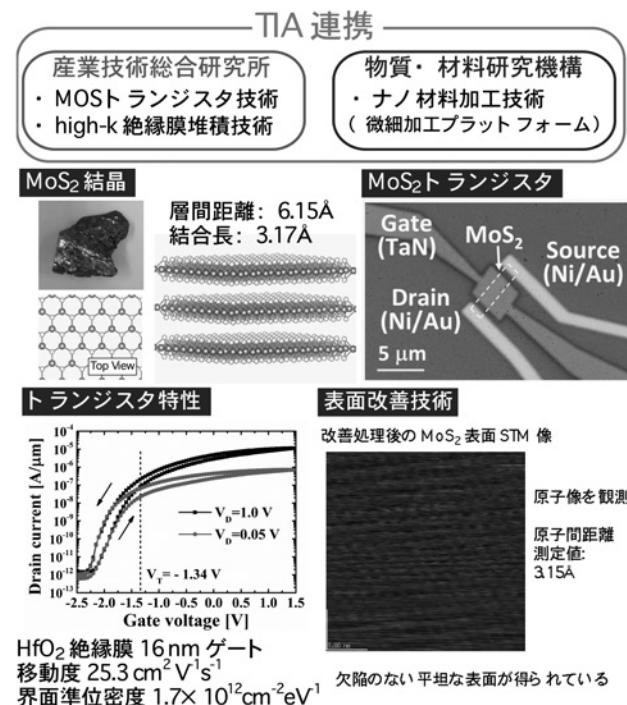

半導体VLSI技術はMOSトランジスタの微細化をドライビングフォースとして進展している。2021年にはそのゲート長は10nmを切る見込みである。IoT(Internet of Things)時代の幕開けを目前に情報処理量の爆発的な増加が見込まれる中、情報処理能力の向上のためにVLSI技術の更なる高度化が要請されている。そのため、MOSトランジスタの技術革新は引き続き重要な研究要素となっている。我々はゲート長5nm世代のトランジスタに必須となる3nm以下の極薄チャネル材料として原子薄膜材料に注目、その技術開発を進めている。対象としている原子薄膜材料はMoS<sub>2</sub>(二硫化モリブデン)である。本研究においてはTIA(Tsukuba Innovation Arena)に参画している産業技術総合研究所と物質・材料研究機構の研究者が有機的に連携し、また両者の保有するナノデバイス試作設備群を活用することで研究の効率化を図っている。

## ■活動内容

### 1. 原子薄膜トランジスタの開発

原子薄膜材料をチャネルとしたトランジスタの性能向上策を検討している。原子薄膜トランジスタには、従来用いられているシリコンとは異なる要素技術が必要となる。MOSトランジスタの心臓部であるゲートを形成する技術について、high-k絶縁膜と原子薄膜材料とのゲート界面制御技術の確立を目指している。

我々は原子薄膜材料の一つであるMoS<sub>2</sub>をチャネルとしたトランジスタを試作、high-k膜としてHfO<sub>2</sub>とAl<sub>2</sub>O<sub>3</sub>との2種について検討を行っている。これまでのところ、HfO<sub>2</sub>絶縁膜を適用したトップゲート型MoS<sub>2</sub>トランジスタにおいて良好な特性が得られており、移動度としては $25.3 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ 、界面準位密度としては $1.7 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$ を達成している。移動度は、一般によく試作されるバックゲート型MoS<sub>2</sub>トランジスタの2倍以上となっており、high-kゲート技術の優位性がわかる。界面準位密度はIII-V族半導体/high-k絶縁膜界面と同等であり、良好な界面が形成できている。

現状の課題としては移動度の向上が望まれること、電極コンタクト技術の確立が必要であるとの2点が挙げられる。これらについても現在鋭意研究を進めている。

### 2. 原子薄膜の表面改善技術

良好な絶縁膜/原子薄膜界面の形成のためには、原子薄膜の初期表面が重要となる。在来の原子薄膜表面に

は少なくない欠陥が存在している。我々は表面欠陥の減少を図るため、真空アニールによる表面改善技術の開発に取り組んでいる。

MoS<sub>2</sub>の表面欠陥評価を、STM(Scanning Tunneling Microscopy)を用いた表面観察によって行っている。MoS<sub>2</sub>の初期表面には多数の欠陥が見られるが、これまでの研究で真空アニールを施すことで表面欠陥を減少させられることがわかっている。これは原子に熱駆動力を与えることで表面原子が再配列され、欠陥が表面テラス端に移動することで実現されていると考えられる。

この表面改善技術と前記界面形成技術とを組み合わせることで、トランジスタ移動度の改善が期待される。現在、表面改善技術を取り込んだデバイス作製プロセスの検討を進めている。

## ■関連情報等

本研究は文部科学省ナノテクノロジープラットフォーム事業(NIMS微細加工プラットフォーム)の支援を受けて実施している。

**■キーワード:** (1)機能性原子薄膜

(2)微細トランジスタ

(3)表面技術