# 半導体レーザの試作に向けた 高反射コーティングの検討

ナノテクノロジー

# SATテクノロジー・ショーケース2025

## ■ はじめに

昨今、データセンタ内の通信トラフィック量や消費電力 の増加が問題視される。現在、高速化・低消費電力化を狙 った光伝送技術が採用されているが、さらなる高速化・低 消費電力化を求めてCPO(Co-Packaged Optics)技術が注 目を集めている。

CPO技術とは、従来の光伝送技術が、光伝送モジュー ルを基板に外付けで実装するのに対して、CPOでは実装 基板上に光伝送モジュールも搭載する。スイッチICから光 ICまでの距離を短縮させることで、電気配線が長いことに よって生じる消費電力を抑え、高速で大容量の光伝送を 低消費電力で可能にする。

このCPO技術の課題として挙げられるのは、半導体レー ザの高い故障率だ。半導体レーザの信頼性は、電子部品 に比べて100倍以上高い。そこで私たちが注目したのが、 量子ドット半導体レーザ(LD:Laser Diode)である。量子ドッ ト半導体レーザは、量子ドット構造により、量子ドットの大き さを制御することで光の波長を制御できる。また、低消費 電力を実現可能なうえ、温度依存性が低いことから、将来 の応用が期待されている。

本発表では、量子ドット半導体レーザの端面加工につ いて検討し、InPにSiO2を成膜して反射率を増強した場合 の膜厚と透過・反射スペクトルの測定結果について報告す る。

# ■ 活動内容

### 1. 成膜

SAMCO社製のプラズマCVD装置PD-220.Sを用いてInP 基板上にSiO。の薄膜を形成した。プラズマCVDは、成膜原 料のガスをプラズマ状態に分解して、活性した状態で化学 反応を行わせる。

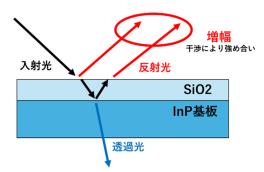

このSiO2薄膜の膜厚は、LD(レーザダイオード)応用を 狙うHRコーティング(図1)を目的とするため、λ/2n=452nm を成膜した。このときnは波長1310nmでのSiO2の屈折率で n=1.447である。HRコーティングは、屈折率の異なる多層 膜による干渉効果を利用している。本実験ではSiO2薄膜表 面での反射光とInP基板表面の反射光によって全体の反 射率が決定される。光の波長に応じた膜厚に調整すること で、特定の波長の光が強く反射され、非常に高い反射率 を得ることができる。

現在私たちが注目している量子ドット半導体レーザの共 振器ミラーに、このような端面加工を施すことで、損失を抑 え、より安定したレーザ出力が期待される。

#### 2. 膜厚測定

膜厚計で膜厚を測定した。測定では、Film Sense社製の 型式FS-4の4波長LEDを用いたシステムを用いた。前述の 通り、LD応用のためSiO。の膜厚は452nmが望ましい。前段 階の成膜の工程の後、452nmに近い膜厚がとれているか 確認した。

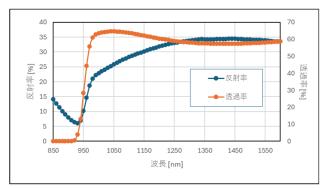

# 3. 透過・反射スペクトル測定

分光光度計はそれぞれの波長ごとの単色光を照射する ことにより、物質固有の透過率や反射率を測定できる。こ れを用いてSiO。を成膜した基板の透過・反射スペクトルを 測定した。結果は以下の図2の通り。まず反射率について、 波長1310nm時点で反射率が極大の34%となることが確認 できる。この反射率の増大からLD応用が見込める結果とな った。また透過率について、波長900nmでバンド間の光吸 収により透過率が0となった。

図1 HRコート反射率増幅の原理

図 2 SiO $2 \times$ 成膜した InP 基板の透過・反射スペクトル

代表発表者 奈須 佑貴(なす ゆうき)

東京理科大学

創域理工学部電気電子情報工学科

〒278-8510 千葉県野田市山崎 2641 問合せ先

> TEL:04-7124-1501 7321150@ed.tus.ac.jp

**■キーワード:** (1) 光実装 (2) 半導体レーザ

(3)量子ドット構造

(4)高反射

■共同研究者:大坪祐馬(東京理科大学)

伊佐早佑大(東京理科大学) 板谷太郎(產業技術総合研究所) 天野建(産業技術総合研究所) 前田讓治(東京理科大学)