# SrTiO<sub>3</sub>自立膜FETの動作実証とドリフト拡散解析

(M2) 田中嵩祐<sup>1,2</sup>, 井上悠<sup>2</sup>, 鬼頭愛<sup>2</sup>, 田村雅史<sup>1</sup>, 井上公<sup>1,2</sup> 東理大創域理工<sup>1</sup>, 産総研<sup>2</sup>

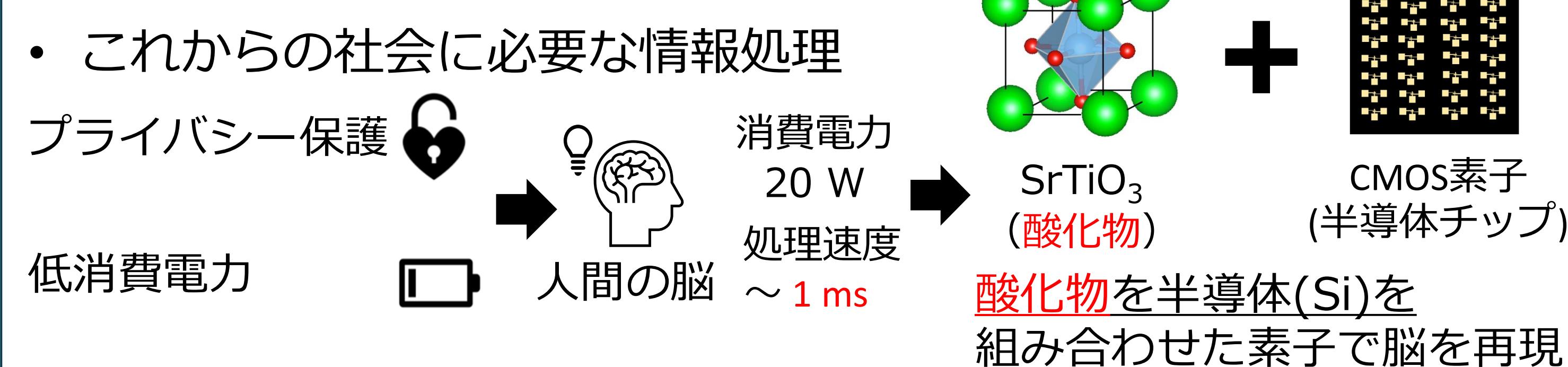

## 1. 研究背景

近年、生成AIの登場は社会に多大な恩恵をもたらしているが、一方でプライバシー保護や莫大な電力消費といった課題も顕在化している。これに対し、人間の脳はわずか20W程度の消費電力で動作し、オフラインでの学習も可能である。我々は、酸化物と半導体素子を組み合わせることで、この脳機能を模倣できることを実証した<sup>[1]</sup>。しかし、酸化物は融点が高いなど、半導体素子との融合が依然として困難である。

目的 半導体素子と酸化物膜素子の融合

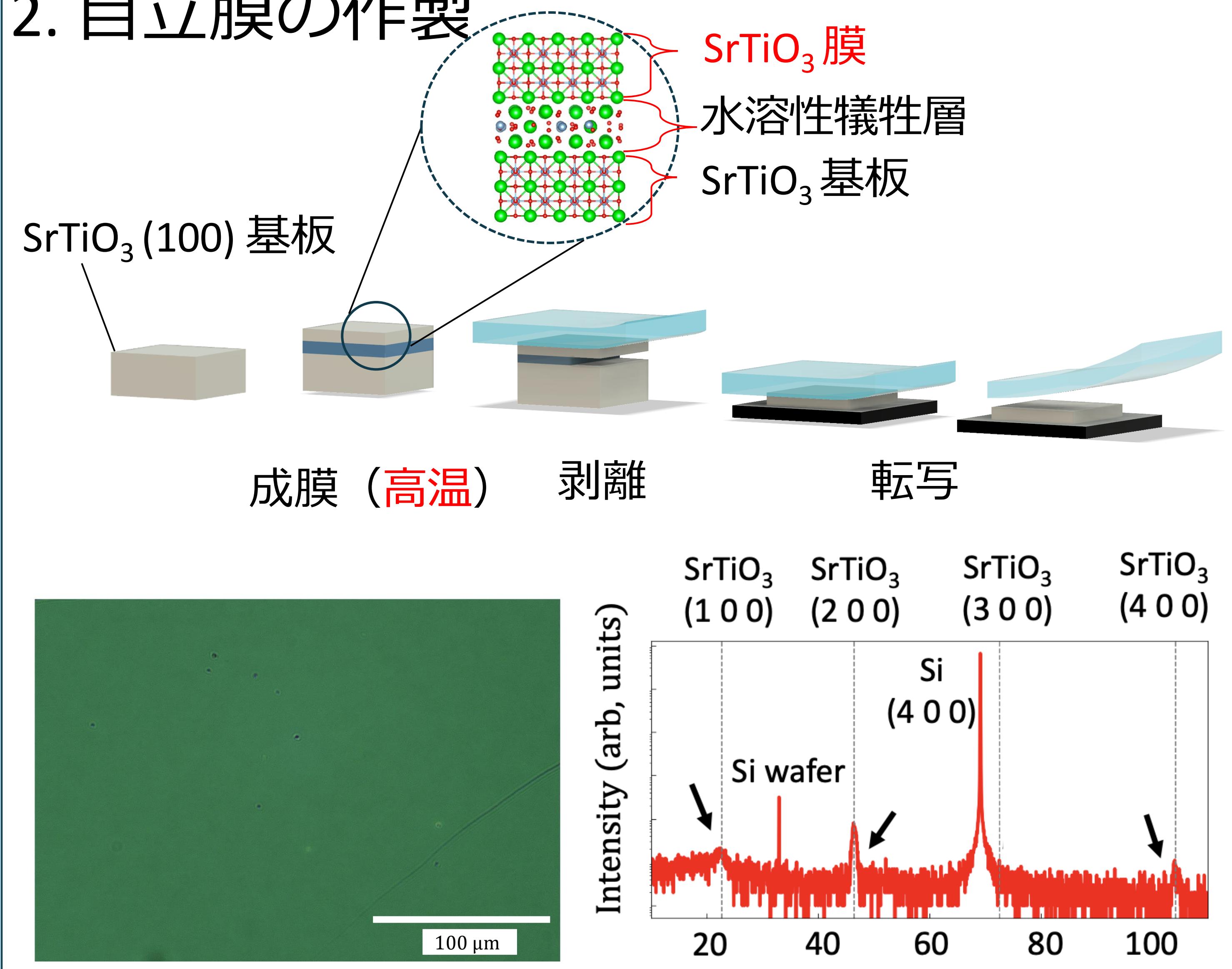

## 2. 自立膜の作製

半導体素子との低温融合に向け、近年報告された<sup>[2]</sup>酸化物自立膜を作製した。パルスレーザー堆積法(PLD)法によりSrTiO<sub>3</sub>基板上に水溶性犠牲層Sr<sub>4</sub>Al<sub>2</sub>O<sub>7</sub>とSrTiO<sub>3</sub>膜を成長させ、水剥離プロセスを経てSi/SiO<sub>2</sub>基板へ転写した。光学顕微鏡およびXRD測定の結果、亀裂の少ない大面積かつc軸配向したSrTiO<sub>3</sub>自立膜の作製を確認した。

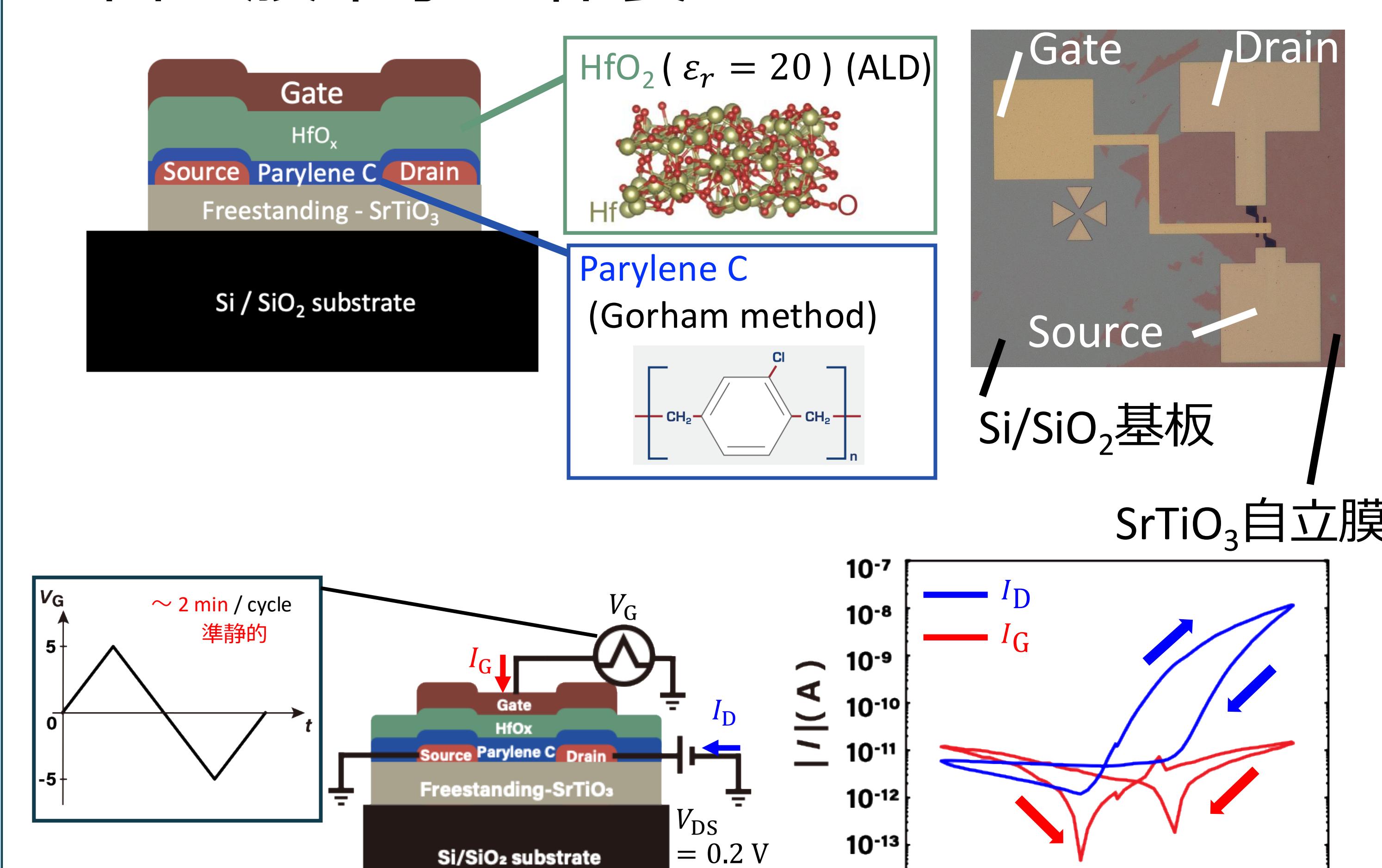

## 3. 自立膜素子の作製

SrTiO<sub>3</sub>自立膜をチャネルとし、Parylene C/HfO<sub>2</sub>積層膜をゲート絶縁膜に用いた電界効果トランジスタ(FET)を作製した。電気的特性評価の結果、ゲートリーク電流は低く抑えられ、ゲート電圧による大きなキャリア変調が観測された。本研究により、これまで報告例のないSrTiO<sub>3</sub>自立膜を用いたFETの動作実証に成功した。

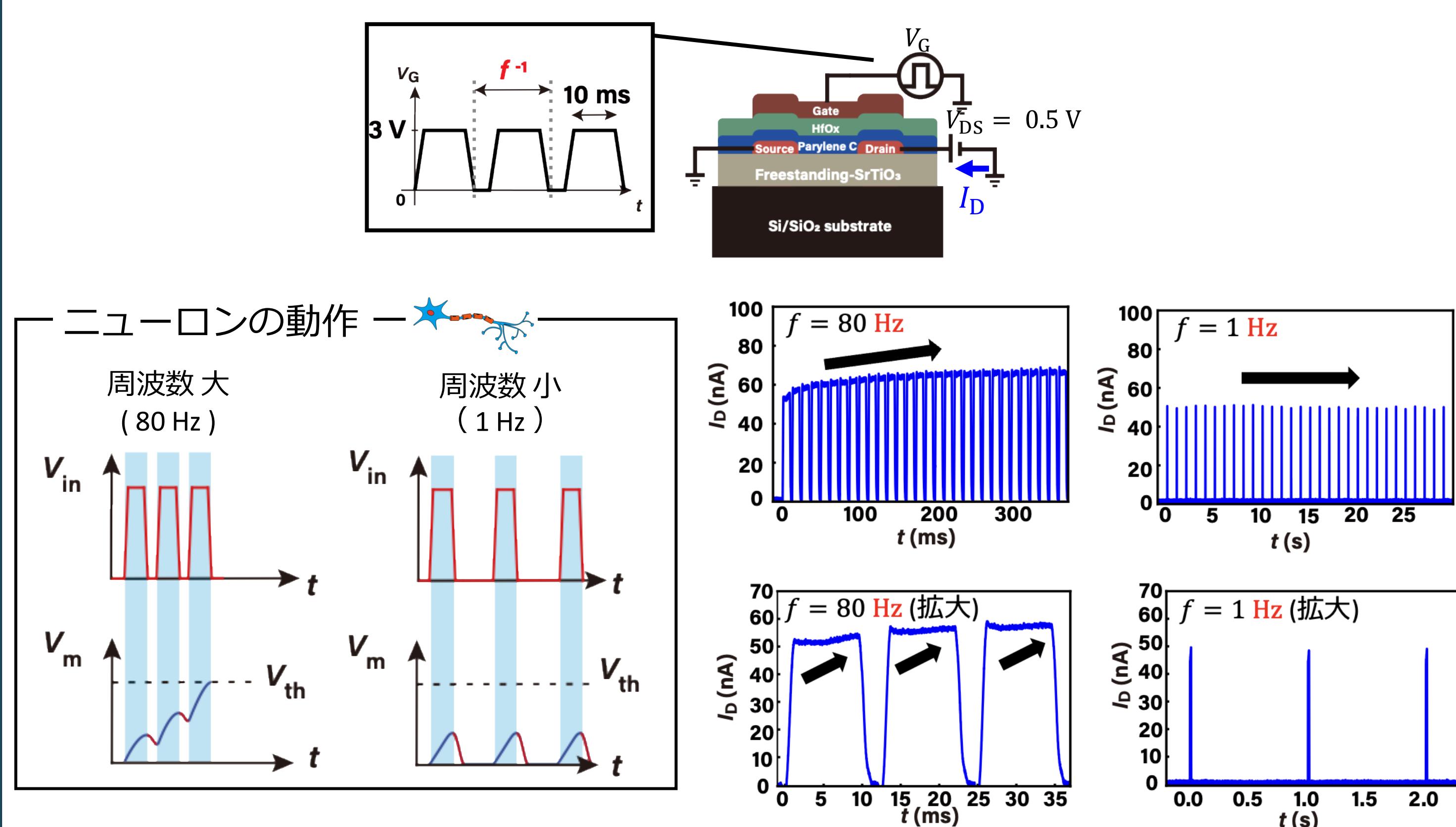

## 4. ニューロン動作の実証

SrTiO<sub>3</sub>自立膜素子にニューロン様パルスを印加したところ、低周波（1 Hz）では応答せず、高周波（80 Hz）でのみ電流が増大することを確認し、生体ニューロンの信号処理機能を模倣しており、本素子の脳機能模倣デバイスとしての高い可能性を示唆している。

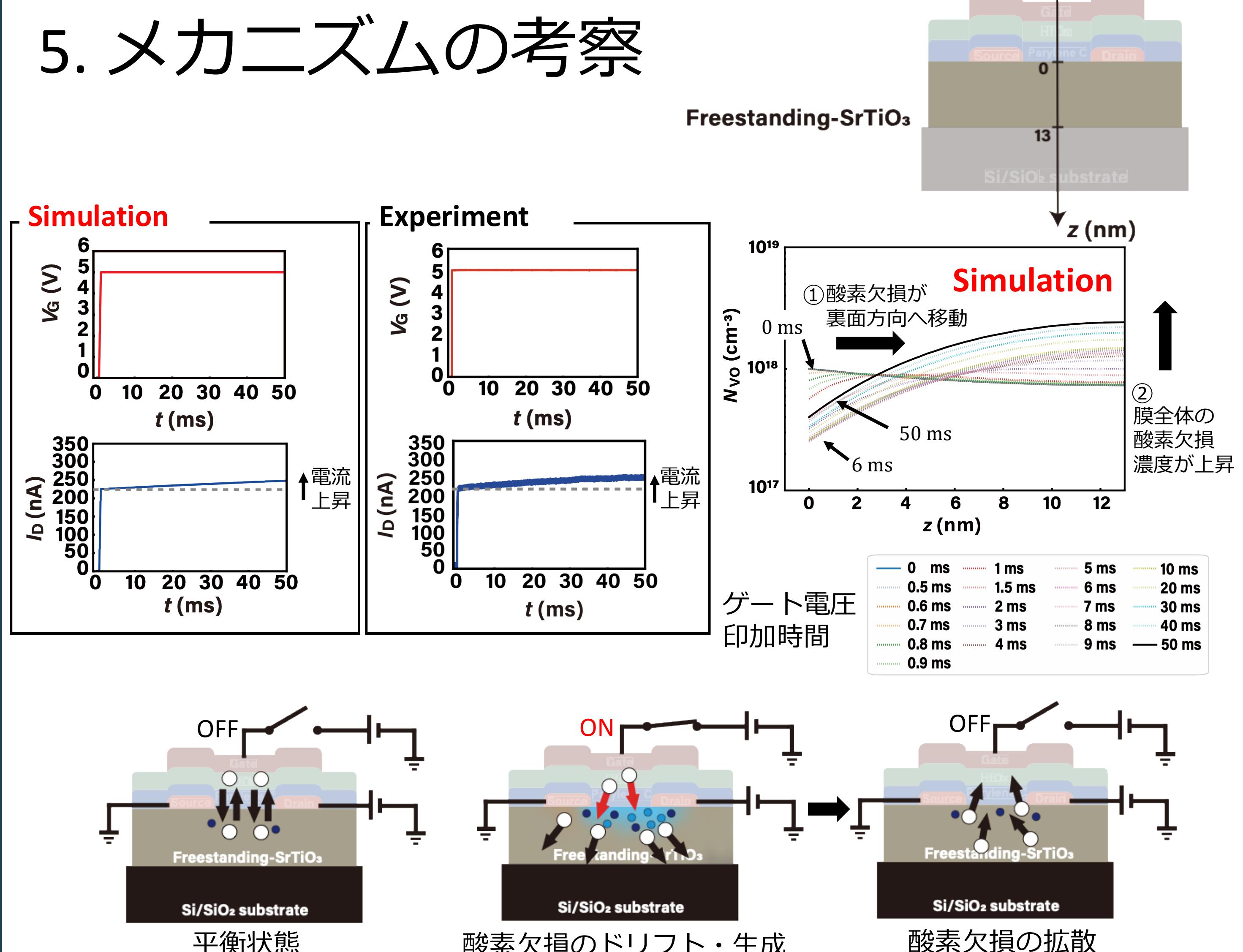

## 5. メカニズムの考察

COMSOLを用いた有限要素解析により動作メカニズムを考察した。一定のゲート電圧を印加した際のドレイン電流をシミュレーションにより求めた。ゲート電圧印加直後の急激な電流上昇は電子の蓄積に起因し、続く緩やかな電流増加は、電界による酸素欠損の膜下部への移動と、それに伴う表面での欠損生成（電子供給）によると考えられる。表面反応を律速過程としたモデルが実験結果を再現したことから、本素子の動作は表面からの酸素欠損供給に支配されていることが示唆された。

## まとめ

- 大面積のSrTiO<sub>3</sub>自立膜の作製に成功

- SrTiO<sub>3</sub>自立膜をチャネルにしたFET動作を実証

- 有限要素法より、動作メカニズムを考察

## 参考文献

- [1] H. Inoue et al., *Adv.Mater.* 37, 2407326 (2025).

[2] D Lu et al., *Nat.Mater.* 15, 1255-1260 (2016).