# SrTiO<sub>3</sub>自立膜 FET の動作実証とドリフト拡散解析

SATテクノロジー・ショーケース2026

## ■はじめに

複合酸化物 SrTiO<sub>3</sub>(STO)は、ニューロン模倣型の超低消費電力デバイス[1]をはじめ、次世代エレクトロニクスのキーマテリアルとして注目されている。一方で、高品質な結晶成長に高温を要するため、CMOS プラットフォームとの直接統合は依然として難しい。近年、水溶性犠牲層を介して複合酸化物自立膜を形成・転写する手法が提案され[2]、低温で多様な基板へ転写可能な新たな集積ルートが開かれた。本研究では、水溶性犠牲層として SrAl<sub>2</sub>O<sub>7</sub> (SAO)を用いて STO 自立膜を作製し、その自立膜をチャネルとする電界効果型トランジスタ(Freestanding STO-FET)を作製・動作実証した。STO 自立膜をチャネルに用いた FET の動作報告はこれまでになく、高温プロセスを回避しつつ CMOS 互換な酸化物機能実装に向けた有効な道筋を示す。

## ■活動内容

### 1. Freestanding STO-FETの作製

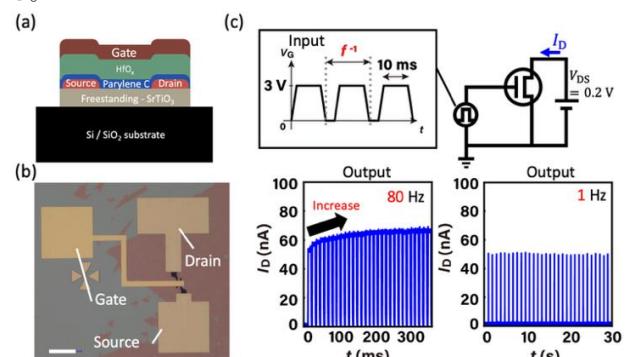

KrF レーザー ( $\lambda=248\text{ nm}$ )を用いたパルスレーザー堆積法(PLD)により、STO 基板上に STO/SAO のエピタキシャル二層膜を成長させた。水に浸して水溶性犠牲層 SAO を選択的に溶解除去し、得られた薄膜を Si/SiO<sub>2</sub>基板へ転写することで STO 自立膜を作製した。ゲート絶縁膜として Parylene C および HfO<sub>2</sub>を用い、自立膜をチャネルとする Freestanding STO-FET を作製した(図(a),(b))。

### 2. Freestanding STO-FETの電気特性評価

電流-電圧特性の準静的測定( $V_{DS} = 0.2\text{ V}$ ,  $V_G = +5\text{ V}$  ~  $-5\text{ V}$ )において、ゲートリーク電流は十分小さく( $I_G < 0.1\text{ nA}$ )、オン-オフ比は  $> 10^3$  を示した。これは従来のバルク STO-FET と整合するスイッチング挙動であり、チャネルが基板から完全に分離された自立構造であっても大きな電流変調が可能であることを実証した。

[1] H. Inoue *et al.*, *Adv. Mater.* **37**, 2407326 (2025).

[2] D Lu *et al.*, *Nat. Mater.* **15**, 1255–1260 (2016).

代表発表者 田中 崇祐(たなか こうすけ)

所 属 東京理科大学 創域理工学研究科

産業技術総合研究所

問合せ先 〒305-8565 茨城県つくば市東 1-1-1

TEL: 080-2202-0758

MAIL: tanaka-tusph@aist.go.jp

### 3. ニューロモルフィックデバイスへの応用

我々はこれまでに、バルクSTO-FETにおいて、ニューロン入力を模した電圧パルス印加時に酸素欠損がドリフト・拡散し、生体ニューロン様の挙動を示すことを報告した[1]。この知見を踏まえ、本研究で作製した素子でも同様の応答を検証した。その結果、Freestanding STO-FETにおいてもパルス印加によりドレイン電流の緩やかな増加が観測され(図(c))、生体ニューロン動作の模倣が可能であることがわかった。さらに、応答の時間スケールは約 1 ms ~ 1 s と、生体ニューロンと同等の範囲であった。

### 4. 有限要素法による動作メカニズムの考察

COMSOL Multiphysics®ソフトウェアを用いた有限要素法によるシミュレーションにより、本デバイスの動作メカニズムは、従来のバルク STO-FET とは本質的に異なることが示唆された。バルク素子ではチャネル内の酸素欠損のドリフトが長い時間スケールに寄与しているが、本デバイスはチャネルの膜厚が極めて薄い(~ 13 nm)ため、ドリフトは速やかに完了する。その結果チャネル表面における酸素欠損の生成反応が新たな律速段階となり、生体ニューロンと同等の長い時間スケールの応答が実現されると考えられる。

図(a) Freestanding STO-FET の断面模式図。(b) デバイスの光学顕微鏡像 (スケールバー: 100 μm)。(c) パルス電圧印加時のドレイン電流の時間応答。

## ■キーワード:

- (1) 複合酸化物

- (2) 自立膜

- (3) パルスレーザー堆積法

## ■共同研究者:

|       |           |

|-------|-----------|

| 鬼頭 愛  | 産業技術総合研究所 |

| 井上 悠  | 産業技術総合研究所 |

| 田村 雅史 | 東京理科大学    |

| 井上 公  | 産業技術総合研究所 |