# 量子ビット制御回路のための MOSFET 極低温動作特性の評価

SATテクノロジー・ショーケース2026

## ■はじめに

量子コンピュータは、現代コンピュータには難しい実用的に重要ないくつかの問題を解くことができる。既にプロトタイプ機は市販されているが、実用的な量子計算を行うには、その基本素子である量子ビットを100万個以上集積する必要があると考えられている。

現在、超伝導型や半導体型の量子ビット素子は、一般に希釈冷凍機内のmK帯温度ステージに設置、動作させる。一方、量子ビットの初期化・操作・読み出しを行う制御機器は室温に設置され、多数の配線を介して量子ビットに接続されている。量子ビットの集積数の増加に伴い、配線ケーブルの本数も増加する。その結果、室温ステージからmK帯ステージへ多量の熱が流入し、希釈冷凍機内の温度が上昇して量子ビットの動作を妨げる要因となる。

この問題に対する解決策の一つとして提案されているのが、冷凍機内で量子ビットを制御するための極低温動作CMOS集積回路の活用である<sup>1)</sup>。このアプローチは、室温と極低温間の配線ケーブルの本数を最小化することを目的としている。このような集積回路およびデバイス技術はCryo-CMOSと呼ばれ、現在活発に研究開発が進められている。

Cryo-CMOS集積回路の実現には、数K帯でのMOSFETの動作特性の解明が不可欠である。しかし、数K以下におけるMOSFETのデバイス特性は室温とは大きく異なる<sup>2)</sup>。特に、界面に由来する欠陥準位の影響が多大になることが特徴的である。

本研究は、これまでに報告例の少ないP型MOSFETにおける界面欠陥の影響を調査することを目的とし、参照用のN型MOSFETも同時に試作、実験的に研究を進めている。

## ■活動内容

### ① N型およびP型MOSFETの作製

N型MOSFETには熱酸化膜SiO<sub>2</sub>(膜厚:約6.3nm)をゲート酸化膜とし、ポリシリコンゲートを用いてバルクSi(100)ウェハ上に作製した。基板の不純物濃度は約 $6 \times 10^{15} \text{ cm}^{-3}$ である。P型MOSFETには熱酸化膜SiO<sub>2</sub>(膜厚:約6.5nm)をゲート酸化膜とし、ポリシリコンゲートを用いてバルクSi(100)ウェハ上に作製した。基板の不純物濃度は約 $2 \times 10^{15} \text{ cm}^{-3}$ である。

### ② N型およびP型MOSFETの3.8~300K帯でのデバイス動作特性の評価

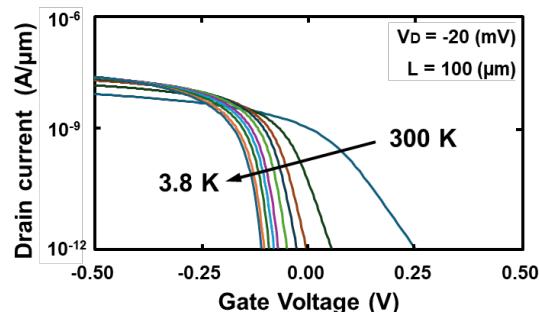

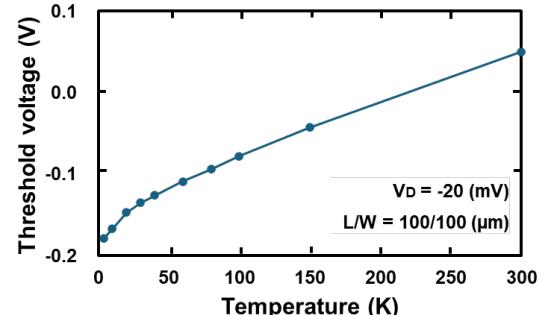

例として図1と図2に作製したP型MOSFETのI<sub>D</sub>-V<sub>G</sub>特性と閾値電圧(V<sub>th</sub>)の温度依存性を示す。この他に移動度、サブスレッショルドスイギングなどの各種デバイスパラメータの算出および評価を実施している。V<sub>th</sub>の温度依存性は従来理論では説明できないものとなっており、界面欠陥の影響が顕在化しているものと考えられる。

図1 P型MOSFETのI<sub>D</sub>-V<sub>G</sub>特性の温度依存性図2 P型MOSFETのV<sub>th</sub>の温度依存性

## ■関連情報等(特許関係、施設、謝辞)

本研究におけるデバイス試作は、産業技術総合研究所・未踏デバイス試作共用ライン(COLOMODO)にて実施された。文部科学省光・量子飛躍フラッグシッププログラム(Q-LEAP)JPMXS0118069228の助成を受けている。

## ■参考文献

- 1) E. Charbon, IEEE Solid-State Circuits Mag. 13, 54 (2021).

- 2) H. Oka, JSAP Rev. 220305 (2022).

## ■キーワード:

- (1) Cryo-CMOS

- (2) 量子コンピュータ

## ■共同研究者:

森 貴洋 産業技術総合研究所・研究チーム長

岡 博史 産業技術総合研究所・主任研究員

森山 悟士 東京電機大学 工学部 電気電子工学科 教授

代表発表者

所 属

問合せ先

香取 匠(かとり たくみ)

東京電機大学工学研究科

電気電子工学専攻 森山研究室

〒305-8568

茨城県つくば市梅園 1-1-1 中央事業所二

TEL:050-3522-9070